Data Flow Modelling in Verilog

Specifications comes first they describe abstractly the functionality interface and the architecture of the digital IC circuit to be designed. Led by some of our top Senior Traders the program includes option theory systems training trading strategy risk management data analysis quant modeling and hands-on trading simulations.

Chapter 3 Dataflow Modeling Ppt Download

Verilog introduces new two-state data types where each bit is 0 or 1 only.

. VLSI Digital System. The various levels of design are numbered and the blocks show processes in the design flow. Verilog code for AND gate using data-flow modeling.

The various levels of design are numbered and the blocks show processes in the design flow. They also decide on how the data should flow inside the chip. The VLSI IC circuits design flow is shown in the figure below.

An example would be the data flow when a processor fetches imaging data from the system ram and executes them. A comprehensive resource on Verilog HDL for beginners and experts large and complicated digital circuits can be incorporated into hardware by using Verilog a hardware description language HDL. Meanwhile the graphics engine will execute post-processed data from the previous batch dumped into another part of memory and so on.

VLSI Design Flow The VLSI IC circuits design flow is shown in the figure below. Specifications comes first they describe abstractly the functionality interface and the architecture of the digital IC circuit to be designed. In succession of International Conferences SPIN-2014 SPIN-2015 SPIN-2016 SPIN-2017 SPIN-2018 SPIN-2019 SPIN-2020 SPIN 2021 9th International Conference on Signal Processing and Integrated Networks SPIN-2022 will be organized by Amity University Noida on.

Then we use assignment statements in data flow modeling. Describes how the Vitis development environment lets you build a software application using the OpenCL API to run hardware kernels on accelerator cards like a Xilinx Alveo Data Center accelerator card for FPGA-based acceleration. We would again start by declaring the module.

Using two-state variables in RTL models may enable simulators to be more efficient. All that a designer need is the. The idea is that algorithms modeled in C can be converted to Verilog if the two languages have the same data types.

Week-6Switch level modelling Week-7Synthesis of combinational logic using verilog Week-8Synthesis of sequential logic. Junior Traders then graduate into real-time trading rotations and a one-on-one mentorship with a Senior Trader. And they are not affecting the synthesis results.

Module AND_2_data_flow output Y input A B. Behavioral modeling is the highest level of abstraction in the Verilog HDL.

Chapter 3 Dataflow Modeling Ppt Download

Chapter 3 Dataflow Modeling Ppt Download

Dataflow Level Verilog Code Of 4 To 1 Multiplexer Mux And Testbench Simulation In Modelsim Youtube

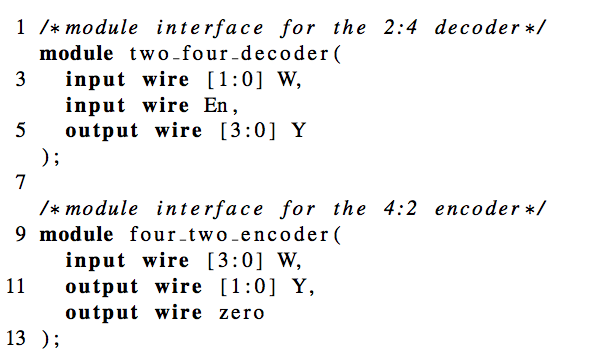

Solved Verilog Code With Comments For The 2 4 Binary Chegg Com

No comments for "Data Flow Modelling in Verilog"

Post a Comment